# 适用于电力杆塔缺陷检测的大功率脉冲电源

白卫1,卢胜标1,刘冲2

(1. 广西电网有限责任公司玉林供电局,广西玉林537000; 2. 南华大学电气工程学院,湖南 衡阳421001)

摘 要:提出一种用于电力杆塔缺陷检测脉冲电源拓扑及其样机实现。该脉冲电源的拓扑采用新型开关器件,可满足脉冲快速、可调需求。电力杆塔缺陷检测需要在几十千伏的电压下产生具有亚纳秒上升时间的脉冲电源,为实现这一点,将传统脉冲电源引入固态开关器件。所提出的脉冲电源设计为由多个堆叠的同轴层组成的拓扑结构,其中每层由包含多个开关器件的印刷电路板(PCB)组成。然后,对所提出的脉冲电源进行 3D 电磁仿真分析,并设计 5 kV 脉冲电源样机,测试样机在  $2.5~\mathrm{kV}$ 、 $50~\mathrm{\Omega}$  负载下可实现  $6~\mathrm{ns}$  的脉冲上升时间,验证所提电源能够产生灵活脉冲波形,从而验证所提出设计方法的有效性。

关键词:缺陷检测;脉冲电源;金属氧化物半导体场效应晶体管;固态开关;纳秒脉冲

DOI:10.19781/j.issn.1673-9140.2022.04.003 中图分类号:TM863 文章编号:1673-9140(2022)04-0020-09

## Research on high-power pulsed power supply used for defect detection of power tower

BAI Wei<sup>1</sup>, LU Shengbiao<sup>1</sup>, LIU Chong<sup>2</sup>

(1. Yulin Power Supply Bureau, Guangxi Power Grid Co., Ltd., Yulin 537000, China; 2. School of Electrical Engineering,

University of SouthChina, Hengyang 421001, China)

Abstract: This paper proposes a pulse power topology and its prototype implementation for power tower defect detection. The pulse power topology adopts new switching devices, which can meet the requirements of fast and adjustable pulse Defect detection of power poles and towers requires the generation of pulsed power supplies with sub-nanose-cond rise times at voltages of tens of kilovolts. To achieve this, traditional pulsed power supplies are introduced into solid-state switching devices. The proposed pulsed power supply is designed as the topology structure which consists of multiple stacked coaxial layers, where each layer consists of a printed circuit board (PCB) containing multiple switching devices. Then, the 3D electromagnetic simulation analysis of the proposed pulse power supply is carried out, and a 5 kV pulse power supply prototype is designed. The test prototype can achieve a pulse rise time of 6 ns under a load of 2.5 kV and 50 Ω, verifying that the proposed power supply can generate flexible pulse waveforms, verifying the effectiveness of the proposed design method.

**Key words:** defect detection; pulse power supply; metal oxide semiconductor field effect transistor; solid state switch; nanosecond pulse

电力杆塔的地脚螺栓是杆塔的结构支撑重要部件,预埋在基座基础中,受到周围介质的侵蚀和电缆

重力以及风动负载的拉拔力和剪切力共同作用[1]。 使用磁致伸缩导波技术是电力杆塔缺陷检测问题解

收稿日期:2021-05-16;修回日期:2021-07-26

基金项目:广西电网有限责任公司科技项目(0002200000075059)

通信作者:白 卫(1986-),男,工程师,主要从事输电线路工程研究;E-mail: 773741924@qq.com

决方法之一,使用脉冲电源激发磁场,利用杆塔的磁致伸缩特性进行检测<sup>[2]</sup>。而磁致伸缩导波技术在电力杆塔检测方面应用需要可产生上升时间在 10 ns 以内脉冲且输出波形可调的电源。而且杆塔所处环境复杂,检测杆塔数量较多,对脉冲电源的使用寿命,便携性等方面具有比固定场合应用更高的要求。目前,成熟的商业功率脉冲电源无法满足电力杆塔检测的需求<sup>[3-6]</sup>。

脉冲电源在固定应用领域(如化工等)发展较快。所施加的高压脉冲的脉冲持续时间和上升时间对化工生产中瞬态等离子体的自由基产率有显著影响,脉冲越短产量越高<sup>[7]</sup>。文献[8]发现将高压脉冲的上升时间从 5.6 ns 减少到 400 ps 时可将实验中化学效率提高 50%以上。虽然传统纳秒脉冲电源化工领域效率很高,但在电力检测应用上缺乏竞争力。传统纳秒脉冲电源是一种具有油触发模块的单线脉冲电源,能够产生最高 50 kV 的脉冲,脉冲持续时间为 0.5~10 ns,上升时间最快为 200 ps<sup>[9]</sup>。然而油和电极的快速腐蚀严重限制了电源的寿命,并导致输出脉冲波形的显著畸变。

半导体开路开关(semiconductor opening switch, SOS)或漂移阶跃恢复二极管(drift step recovery diodes, DSRD) 脉冲源可以产生快速上升的 脉冲,并可满足上述电力杆塔检测的部分需求,但这 些脉冲源的输出波形通常只有轻微的可调性[10]。 磁脉冲压缩(magnetic pulse compressor, MPC)脉 冲源也是如此,它使用饱和磁性元件来代替 SOS 或 DSRD 二极管,但其波形灵活性较差,通常脉冲产生 速度慢[11]。雪崩晶体管 Marx 发生器产生脉冲上 升时间短,但通常输出低功率、低电压,并且其输出 波形也不能灵活调整[12]。为了实现能够提供极其 灵活的脉冲波形的脉冲源,文献[13]提出一种基于 固态开关的 Marx 发生器,但此脉冲电源的典型上 升时间为 10~20 ns,依然无法满足全部需求。为解 决上述问题,本文基于固态开关器件设计新的脉冲 电源,以优化脉冲电源的快速性、灵活性及便携性。

# 1 脉冲电源工作原理

# 1.1 工作模式

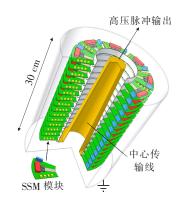

脉冲电源结构如图 1 所示,类似于线性变压器

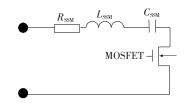

驱动,由多个串联的圆形层组成。每一层都由固态 开关模块(spring+springmvc+mybatis,SSM)并 联组成,其中,每个 SSM 由金属—氧化物半导体场 效应晶体管(metal-oxide-semiconductor field-effect transistor, MOSFET)、开关驱动器、电容和辅助电 路组件组成,SSM 模块的电路结构如图 2 所示,与 文献[14]中提出的一般固态脉冲电源不同,触发隙 和电容由 SSM 代替,并且在开关—电容器组合、中 心同轴传输线之间放置一条短传输线。

图1 脉冲电源结构

Figure 1 Pulse power supply structure

图 2 SSM 模块电路结构

Figure 2 SSM module circuit structure

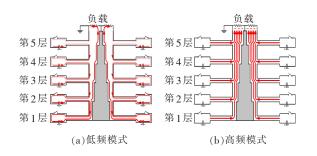

脉冲电源工作模式如图 3 所示,包含低频和高 频模式。

1)低频模式。当脉冲的上升时间明显长于这些脉冲通过电源结构的传播时间时,电源中的脉冲反射可以被忽略。在此情况下,电源的工作模式可以通过电路电流来分析,这时电源与常规 Marx 发生器原理一致,每一层的电容器通过开关的动作串联产生脉冲。

2)高频模式。当脉冲的上升时间明显短于这些脉冲通过电源结构的传播时间时,脉冲反射变得重要。在此情况下,电源的工作模式通过行波来分析,这时由模块产生的脉冲波通过模块的传输线传播,并进入中心同轴传输线。当传输线的阻抗匹配时,所有波在输出端叠加。

图 3 脉冲电源工作模式

Figure 3 Pulse power supply working mode

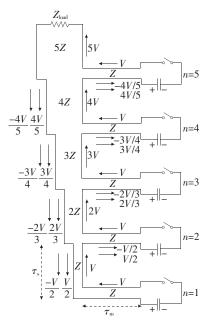

#### 1.2 阻抗匹配

脉冲电源阻抗匹配分析如图 4 所示,电源有 5 个工作层,每层由  $N_m$  个 SSM 模块组合而成。因此,每一层的输出阻抗为

$$Z = \frac{Z_{\mathrm{m}}}{N_{\mathrm{m}}} \tag{1}$$

其中, $Z_m$  是一个模块的传输线阻抗。中心同轴传输线用一个简单的阻抗表示,称之为中心阻抗  $Z_c$  。该中心阻抗从最低层的 Z 处开始,每层增加 Z。因此,中心传输线  $Z_{C_n}$  的第 n 层阻抗可以表示为

$$Z_{Cn} = nZ \tag{2}$$

脉冲电源的输出阻抗为

$$Z_{\text{out}} = N_s Z \tag{3}$$

式中  $N_s$  为总层数,阻抗匹配要求负载阻抗应与输出阻抗相同。

图 4 脉冲电源阻抗匹配分析

Figure 4 Impedance matching analysis of pulse power supply

除阻抗匹配外,触发电源模块的时序也很重要。如:图 4 中第 1 层一旦被触发并向其传输线注入脉冲,则第 1 层延迟  $\tau_m$  后到达中心同轴传输线,再延迟  $\tau_s$  到达与第 2 层的交汇点。为了实现电源的完美运行,来自第 1、2 层的脉冲应该在该交点处同时到达。因此,每层都应该以  $\tau_s$  的延迟来触发。

在图 4 中,从电源中的第 n 层沿中心同轴传输线向下为(n-1)Z 的阻抗,向上为 nZ 的阻抗,这导致脉冲会反射回到本身的传输线中,并且会沿第 n-1、n+1 层的方向传输到中心同轴传输线中。同理,沿中心同轴传输线垂直传播的脉冲只要遇到中间层就会被反射和传输。但是只要满足式(2),除了在负载方向上行进的波之外,所有反射和透射波都被抵消(反射和透射波的幅值见图 4)。总之,为了产生完美的波形,必须满足条件:中心同轴传输线满足式(2);满足与触发阶段相关的时间限制;负载阻抗等于电源的输出阻抗。

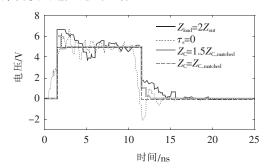

在 LTspice 中对图 4 电路进行仿真,以显示不满足阻抗匹配的影响。不同负载阻抗以及无触发延迟的仿真结果如图 5 所示,可知不满足上述任一条件都会使得输出波形畸变。

图 5 脉冲电源等效电路的 LTspice 仿真结果

Figure 5 LTspice simulation results of pulse

power equivalent circuit

#### 1.3 脉冲电源对比

除了用固态开关模块代替触发模块之外,所提出的电源与常规固态脉冲电源不同之处是在开关模块和中心同轴传输线之间增加了短传输线。

假设没有短传输线,则每个模块的阻抗由开关、电容器和开关模块寄生电感的阻抗决定,模块阻抗值很小,最初的固态脉冲电源依此设计。但在所研究的情况下输出阻抗远远低于产生瞬态脉冲产生所需的阻抗,因此,选择插入传输线实现高输出阻抗 $(100\sim300~\Omega)$ ,而开关模块的阻抗由该传输线决

定,这使得设计更加自由。此外,传输线将限制每个模块的开关电流,可确保不会超过商用 MOSFET 开关的电流限制。

# 2 脉冲电源仿真设计

### 2.1 仿真模型

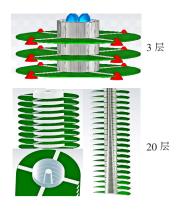

为研究固态脉冲电源在实际应用中的设计,基于 CST MWS 平台进行 3D 电磁仿真。仿真中将印刷电路板(printed circuit board, PCB)制成圆盘,由导电金属环连接和堆叠,这些环构成中心同轴传输线的外导体,光滑的锥形金属导体为中心传输线的内导体。在 PCB 平台上,金属条构成传输线,将中心同轴传输线连接到开关模块(位于每个 PCB 盘的边缘),每个开关模块都用一个理想脉冲电压源建模。

用于仿真的电源模型有 3 层、20 层这 2 种模型,如图 6 所示。根据式(1)~(3),得出每个层阻抗 Z 为 5  $\Omega$ ,每个模块阻抗  $Z_m$  为 20  $\Omega$ 。对于 3 层仿真模型,阻抗匹配情况的仿真结果如图 7 所示。

图 6 脉冲电源 3D 电磁仿真模型

Figure 6 3D electromagnetic simulation model of pulse power supply

图 7 3 层脉冲电源 3D 电磁仿真结果

Figure 7 3D electromagnetic simulation result of 3-stage pulse power supply

由图 7 可知,输出波形是输入波形的 3 倍,波通过电源结构传播造成延迟。仿真输出上的小振荡是由构成负载电阻之间轻微的不匹配所导致。

### 2.2 中心同轴传输线

如文 1.2 中所述,中心同轴传输线的阻抗应随 固态脉冲电源的每一层而增加,以保持阻抗匹配。 中心阻抗可以表示为

$$Z_{Cn} = \frac{1}{2\pi} \sqrt{\frac{\mu_0 \mu_r}{\epsilon_0 \epsilon_r}} \ln \frac{D}{d_n}$$

(4)

式中  $\mu_0$  为绝缘介质的真空度;  $\mu_r$  为相对磁导率;  $\epsilon_0$  和  $\epsilon_r$  为介电常数;  $D \cdot d_n$  分别为中心同轴传输线的外径、内径。

为了保持内部结构的稳定和刚性,最薄处(最高阻抗)的直径约为 10 mm。因此,外环的最小直径至少应为 53 mm,才能获得足够的输出阻抗。改变中心同轴传输线的内导体直径可以通过阶梯或平滑过渡来完成(图 1 表示平滑转接,图 3 表示阶梯转接)。在理想情况下,使用阶梯转接会在 2 层之间产生恒定的特性阻抗,这意味着脉冲可以不失真地从一层传输到下一层。缺点是在转接点处存在尖锐边缘,导致高压绝缘设计不佳。这可以通过使用平滑表面来解决,但是随后阻抗在 2 层之间逐渐改变,这可能会使脉冲失真。折衷的选择是使用阶梯型导体,但具有圆边。然而,仿真结果表明,采用阶梯形或光滑内导体时 20 层电源的输出脉冲波形没有显著差异。

### 2.3 开关模块传输线

每个脉冲电源层由 PCB 制成。除模块外,这些层还将包含控制和电源电路。根据开关模块和中心同轴传输线之间的传输线的长度,PCB 上将保留大量未使用的空间。一种常见的做法是将此空白区域用作接地屏蔽。然而这样的接地层可看做寄生电容,这种寄生电容可以改变模块传输线的阻抗,并且可能具有其他不利影响。

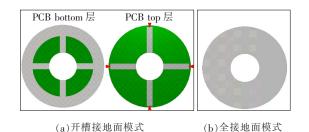

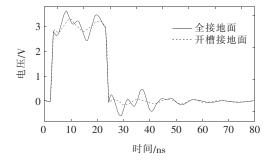

在设计中,考虑 PCB 上接地面的 2 种不同布局,即全接地面和开槽接地面,如图 8 所示。

1)PCB 传输线宽度决定其特性阻抗。如图 8 (b)所示,传输线是由一条导电带组成的,这种结构称为微带(microband),宽度可以用惠勒公式<sup>[15]</sup>来计算。当 PCB 厚度为 1.55 mm、金属厚度为 35

μm、PCB 基板的介电常数为 4.5 时,传输线中金属带的宽度应为 10.6 mm,以满足所需的 20 Ω 阻抗,在仿真中使用此宽度。当使用图 8(a)所示的开槽接地面时,传输线不再是微带线,这将使其特性阻抗增加约 10%。

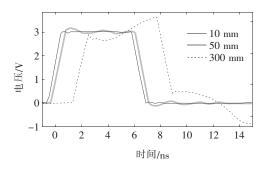

2) PCB 传输线长度若太长, PCB 尺寸必须增大,则层与层之间的耦合电容将会增加。具有不同长度 PCB 传输线的 3 层模型(使用全接地面布局)的仿真波形如图 9 所示,可知一条 10 mm 的传输线已经足够用作传输线。从图 9 仿真结果中观察到的另一个现象是,对于较长的传输线长度,脉冲变得失真。为了找到失真的来源,比较不同接地面布局与不同长度传输线仿真,如图 10 所示,即开槽布局引

图 8 PCB 接地面布局模式

Figure 8 PCB ground plane layout modes

图 9 不同传输线长度的仿真结果

Figure 9 Simulation results of different transmission line length

图 10 不同接地面的仿真结果

Figure 10 Simulation results of different ground planes

入轻微的阻抗失配,使开槽接地面产生的脉冲失真度最小。这表明层与层之间的耦合电容可能是长传输线下脉冲失真的原因。本文折衷选择 40 mm 作为 PCB 传输线长度。

# 2.4 阻抗匹配与寄生效应

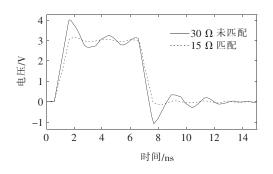

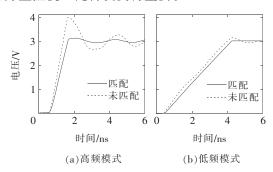

负载阻抗对输出波形的影响如图 11 所示。若负载匹配,则脉冲是平缓的;若负载不匹配,则脉冲显示振荡。这些振荡是由不匹配负载上的脉冲反射引起的。

图 11 阻抗匹配仿真对比

Figure 11 Impedance matching simulation comparison

在图 11 所示的结果中,高频模式下脉冲的上升时间明显较短,阻抗匹配非常重要;低频模式下脉冲上升时间较长,阻抗匹配相对就不重要。2 种模式的结果如图 12 所示,其中低频模式的上升时间为 5 ns,此种情况下的阻抗匹配不重要。当由完整的 20 层固态脉冲电源产生 5 ns 脉冲时,上升时间显著缩短,并且阻抗匹配再次变得重要。

图 12 不同上升时间下阻抗匹配仿真对比

Figure 12 Comparison of impedance matching simulation under different rise times

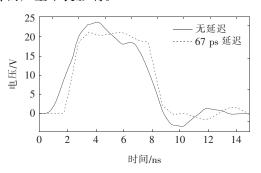

另一个设计标准是第 n 层相对于第 n-1 层应该产生具有一定延迟的脉冲,仿真中该延迟为 67 ps,对完整 20 层固态脉冲电源的影响如图 13 所示。当设置为无延迟时,脉冲变得失真,因为固态脉冲电

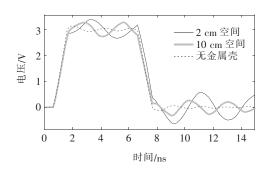

源结构中的波并不同时到达交点。3D 电磁仿真结果与图 4 中 LTspice 仿真结果非常相似,但 3 层仿真模型中这种差异不明显。对于较小的固态脉冲电源结构,脉冲延迟影响变得不重要。在电源周围的外壳用于设备保护或电磁干扰屏蔽,不同外壳结构下的仿真结果如图 14 所示,可知增加外壳会因电容耦合而产生不良影响。

图 13 不同延迟时间仿真对比

Figure 13 Comparison of different delay time simulations

图 14 不同金属外壳间距仿真对比

Figure 14 Simulation comparison of spacing between different metal shells

# 3 脉冲电源样机实现

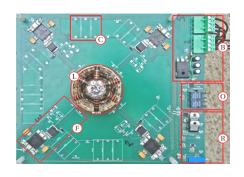

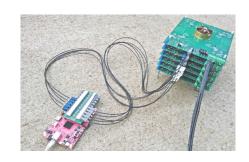

设计一个 5 kV 的 5 层脉冲电源样机,每层由 4 个 SSM 组成,中心传输线为锥形。

#### 3.1 开关器件选型

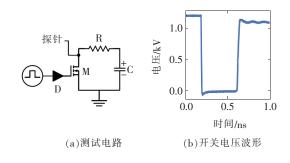

脉冲上升时间设计目标为 1 ns 或更少,场效应 晶体管开关是 SSM 的合理选择。根据给定每层电 压的要求,在不同电压(漏极一源极和栅极一源极) 和电流下测试多款 MOSFET。本文所使用的测试 电路如图 15 所示,被测 MOSFET 通过电阻对电容 放电,开关开通时评估 MOSFET 的开关速度,再用 探针表示的点进行测量;使用 IXYSRF 的 IXR-FD630 作为 MOSFET 栅极驱动器。在开关选型 时,使用最高非破坏性栅极电压(30 V)获得最快的开关速度,而在最终的样机中,必须使用较低的安全电压。根据测试结果,最终选择 Cree 的C3M0075120J MOSFET作为开关器件,其最大电压为1200 V。

图 15 MOSFET 测试电路及开关电压波形 Figure 15 MOSFET test circuit and switching voltage waveform

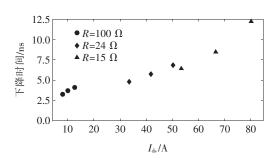

C3M0075120J MOSFET 的开关速度与负载以及开关电流的关系如图 16 所示,在 3 种不同的漏源电压(800、1 000、1 200 V)下测试每种负载;为了减少上升时间,可以使用较低的单层电压或者较高的PCB 传输线阻抗,后者可以通过增加每层的输出阻抗或者使用更多的开关器件来实现;样机中采用增加每层输出阻抗的方法。

图 16 不同负载电阻、电压下的 C3M0075120J MOSFET 开关速度和漏极电流

**Figure 16** C3M0075120J MOSFET switching speed and drain current under different load resistance and voltage

#### 3.2 能量储存和层间高度

若要缩短脉冲的上升时间,则不仅需要快速开关器件,还需要具有低寄生电感的电容器。因此,样机中使用多个陶瓷电容并联,并尽可能靠近开关。假设脉冲不超过 100 ns,可以接受 10% 电压降,则每层需要大约 200 nF 的电容。此外,为了在每个平台上放置电容器和其他元件,选择 20 mm 的层间高度,这为元件和高压隔离提供了足够的空间,同时使

固态脉冲电源空间结构尽可能紧凑。

#### 3.3 电容器放置和充电

SSM 的开关置于电容器的两边,当开关连接到电容器的"一"端时,称为负端开关(图 3);另一种选择是使用正端开关,开关连接到电容的"+"端。在样机中使用负端开关,以便于测量和控制。

脉冲之间所有层上的电容器需充电至 1 kV 左 右,为此,可以采用文献[16]中带二极管的自举电 路。每层上的第 2 个半导体开关(不是 SSM 的一部 分)将电容器的负端从该层接地,因此,充电电流可 以通过二极管流向电容器的正端。该系统效率高, 并且能够通过将容性负载拉至地对其进行放电,还 可通过反并联二极管对层进行旁路,因此,不需要同 时切换所有层就可以输出灵活的脉冲波形。

### 3.4 控制模块

使用 TUL PYNQ Z2,基于 Xilinx Zynq 7000 内核现场可编程门阵列 (field-programmable gate array,FPGA)为各层产生触发脉冲,再使用 HFBR 光纤连接将 FPGA 连接到各层。FPGA 运行在 200 MHz 的时钟频率上,产生的信号时间分辨率为 5 ns。由于受到光纤以及所用驱动器输入延迟的限制,故最短脉冲为 20 ns。

### 3.5 PCB 布线

固态脉冲电源每层开发的 PCB 如图 17 所示,每一层由 4 个开关管("F")、自举充电电路("B")、低压配电("R")和触发器/驱动器电路("O")组成。此外,若需超过 100 ns 的长脉冲,则可在印刷电路板上的"C"点安装额外的薄膜电容器。每个 SSM由 MOSFET 和驱动器组成,在输出端有一条 5.8 mm 宽的 PCB 传输线,输出阻抗为 40 Ω;如文 2.4 中所述,底部接地层根据开槽接布局进行配置;印刷电路板的底部还包含陶瓷脉冲形成电容,电源通过"B"处的电线提供给顶层。在"O"处,2 个光纤接收器从 FPGA 控制板接收信号,用于充电或脉冲模式;充电信号触发"B"处的充电场效应晶体管,而脉冲信号触发 4 个模块。最后,一个在顶层的负载连接到"L"处的中心同轴传输线。

4 个相等长度的传输线从"O"开始,朝向每个 SSM,让触发信号同时到达所有 4 个模块。在完成 的印刷电路板中,单个 SSM 的触发时间到达之间的差异最多为 800 ps。除延迟外,从脉冲发生器到 MOSFET 模块路径中的所有器件都会产生一些抖动(连续脉冲之间的延迟差异),从脉冲发生器到光纤再到 SSM 的最大抖动约为 200 ps,抖动明显短于上升时间。

图 17 脉冲电源 PCB 板

Figure 17 PCB board of pulse power supply

完全组装好的固态脉冲电源样机如图 18 所示,相比同级别传统脉冲电源<sup>[10]</sup>,其体积缩小了 60%以上,满足电力杆塔缺陷检测的便携性需求。中心同轴传输线的内导体由铜片制成,外导体由铜环制成。黄铜环使用金属夹连接到每个层的顶部和底部,负载可以连接在顶层和中心导体之间,使用 50 Ω 的匹配负载和大约 100 Ω 的不匹配负载。

图 18 脉冲电源原理样机

Figure 18 Principle prototype of pulse power supply

# 4 测试分析

当采用固态脉冲电源样机进行测量时,均使用 LecRoy PPE 6 kV(400 MHz 带宽,6 pF)探头和 LecRoy Wavertunner 620 zi(2 GHz,10 Gs/s)数字 存储示波器。

#### 4.1 常规脉冲

由于 HFBR 光纤系统中设备间的差异,使得固

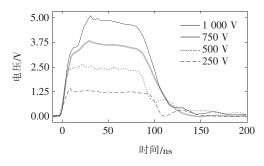

态脉冲电源每层之间的同步偏差高达 15 ns。测试中用 FPGA 每层延迟 5 ns 来补偿这种偏差,但层与层之间的偏差依旧保持在几纳秒间。输出脉冲在250个测量脉冲之间的最大抖动小于 2 ns,标准差仅为 300 ps。

不同充电电压的输出脉冲波形如图 19 所示,所有层同时触发,在 500 V以上层电压的结果中可以看到一些抖动。这是由 MOSFET 驱动器中的振荡而引起的,驱动器不能正确地开通 MOSFET 开关。这些振荡是由高压脉冲耦合到开关驱动器的干扰引起的,必须开发更好的驱动电路克服此问题。

图 19 不同电压下原理样机的测试结果

Figure 19 Test results of the principle prototype under different voltages

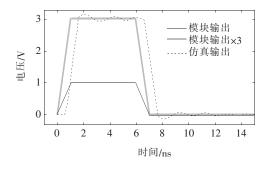

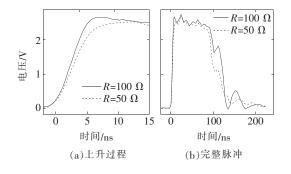

上升时间是针对 2.5 kV 输出电压进行评估的,如图 20 所示,比较匹配负载(50 Ω)和不匹配负载(100 Ω)之间的上升时间。不匹配的较高电阻负载会产生一些过冲和稍快的上升时间,这与图 12 的仿真结果相匹配。使用匹配负载的上升时间平均为6.2 ns,使用不匹配负载的平均上升时间为 4.9 ns。根据匹配和不匹配负载的结果,还可以得出结论,在所开发固态脉冲电源样机中,由于不匹配导致的反射几乎不可见,信号幅值几乎相同。脉冲上升时间达到了 10 ns 以内的设计要求。

图 20 不同阻抗匹配下原理样机的测试结果

Figure 20 Test results of the principle prototype under different impedance matching

#### 4.2 可调脉冲

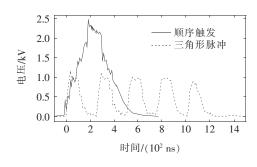

样机能够触发单层以获得灵活的脉冲形状,按顺序并带有延迟触发各层的结果如图 21 所示,非输出层通过充电二极管旁路。在顺序出发、三角形脉冲模式下,将 50 Ω负载连接到电源,因并非所有层同时投入使用,故该器件阻抗不匹配;此外,通向未使用旁路层的路径是一条长的不匹配路径,因此,这些效应解释了可调波形模式下的振荡原因。

图 21 可调脉冲示例

Figure 21 Adjustable pulse example

总之,固态脉冲电源样机工作在低频区,阻抗匹配不是很关键,可以实现 5~6 ns 的脉冲上升时间和灵活的输出脉冲,且电源体积的大大缩小实现了高功率密度。在下一步研究中,可利用改进的栅极驱动电路和层间更好的同步来更快地切换 SSM,可得到更快的上升时间和更好的输出波形。

# 5 结语

本文提出了一种基于固态开关可以实现电力杆塔缺陷检测快速、可调、便携需求的脉冲电源。基于最初的固态脉冲电源概念,增加了传输线和场效应晶体管开关;所提出的脉冲电源由一条中心同轴传输线组成,包含4个SSM模块的印刷电路板馈电;给出了一个20层的3D电磁仿真设计。仿真结果表明,固态脉冲电源工作良好,但在设计中必须小心确保阻抗匹配,并将寄生效应降至最低。最后,设计并实现了一个5层5kV的原理样机,该样机实现了5~6 ns的脉冲上升时间,并且可以产生灵活的脉冲波形。增加更多层可以提高输出电压,由于会增加输出阻抗,因此,可以相应地调整每层模块的数量以满足预期应用的要求。为了获得更好的脉冲参数,在下一步研究中,需要改进开关驱动电路以及SSM模块和固态脉冲电源每层之间的同步问题。

### 参考文献:

[1] 周开河,吴忠平,朱艳伟,等. 复合材料电力杆塔研究进展[J]. 高科技纤维与应用,2021,46(1):68-74.

ZHOU Kaihe, WU Zhongping, ZHU Yanwei, et al. Research progress of composite power pole and tower[J].

High-Tech Fiber and Application, 2021,46(1):68-74.

[2] 肖阳,胡洋,田盈,脉冲涡流扫查技术在炼油装置腐蚀检

- 测上的应用[J]. 石油化工腐蚀与防护,2021,38(2):32-35.

XIAO Yang, HU Yang, TIAN Ying. Application of pulsed eddy current in corrosion detection of refining unit[J]. Corrosion & Protection in Petrochemical Indus-

- [3] 张小龙,张子健,柴军辉,等.基于超声导波和脉冲涡流技术的承压设备腐蚀检测[J].无损检测,2021,43(4):77-81.

try, 2021, 38(2): 32-35.

- ZHANG Xiaolong, ZHANG Zijian, CHAI Junhui, et al. Corrosion detection of pressure equipment based on ultrasonic guided wave and pulsed eddy current technology[J]. Nondestructive Testing, 2021, 43(4):77-81.

- [4] 焕炀,余岳辉,胡乾,等. RSD 开关在脉冲电源中的应用研究[J]. 中国电机工程学报,2003,23(11):23-28.

LI Huanyang, YU Yuehui, HU Qian, et al. Application of RSD switch in pulse power supply[J]. Proceedings of the CSEE,2003,23 (11):23-28.

- [5] 李凯,胡文斌,刘宇芳. 纳秒级高压脉冲电源的研究[J]. 电力电子技术,2021,55(3):71-73.

LI Kai, HU Wenbin, LIU Yufang. Research on nanosecond high voltage pulse power supply[J]. Power Electronics,2021,55(3):71-73.

- [6] 杨勇,梅丹华,段戈辉,等. 不同电源激励 Ar 同轴介质阻 挡放电特性对比[J]. 高电压技术,2020,46(12):4355-4364. YANG Yong, MEI Danhua, DUAN Gehui, et al. Com

- parison of discharge characteristics of Ar coaxial dielectric barrier discharge dirven by different power supplies [J]. High Voltage Technology, 2020, 46 (12): 4355-4364.

- [7] ONO RYO, NAKAGAWA YUSUKE, ODA TETSUJI.

Effect of pulse width on the production of radicals and excited species in a pulsed positive corona discharge[J].

- Journal of Physics D: Applied Physics, 2011, 44 (48): 485201.

- [8] HUISKAMP T, HOEBEN W, BECKERS F, et al. (Sub)nanosecond transient plasma for atmospheric plasma processing experiments: application to ozone generation and NO removal[J]. Journal of Physics D: Applied Physics, 2017, 50(40): 405201.

- [9] HUISKAMP T, VOETEN S J, VAN HEESCH E J M, et al. Design of a subnanosecond rise time, variable pulse duration, variable amplitude, repetitive, high-voltage pulse source[J]. IEEE Transactions on Plasma Science, 2014,42(1):127-137.

- [10] GREKHOV I V. Pulse power generation in nano- and sub-nanosecond range by means of ionizing fronts in semiconductors; the state of the art and future prospects[J]. IEEE Transactions on Plasma Science, 2010, 38(5):1118-1123.

- [11] DRIESSEN A, BECKERS F, HUISKAMP T, et al. Design and implementation of a compact 20-kHz nanosecond magnetic pulse compression generator[J]. IEEE Transactions on Plasma Science, 2017, 45 (12); 3288-3299.

- [12] LI C X, WANG E Z, TAN J W, et al. Design and development of a compact all-solid-state high-frequency picosecond-pulse generator[J]. IEEE Transactions on Plasma Science, 2018, 46(10): 3249-3256.

- [13] HOCHBERG M, SACK M, HERZOG D, et al. A fast modular semiconductor-based marx generator for driving dynamic loads [J]. IEEE Transactions on Plasma Science, 2019, 47(1):627-634.

- [14] STYGAR W A, LECHIEN K R, MAZARAKIS M G, et al. Impedance-matched Marx generators[J]. Physical Review Accelerators and Beams, 2017, 20;040402.

- [15] WHEELER H A. Transmission line properties of a strip on a dielectric sheet on a plane[J]. IEEE Transations on Microwave Theory and Technology, 1977, 25 (8):631-647.

- [16] REDONDO L M, TAVARES P, SILVA J F, et al. All silicon marx-bank topology for high-voltage, high-frequency rectangular pulses [C]// IEEE 36th Power Electronics Specialists Conference, Aachen, Germany, 2005.